Nell'ultimo anno, sono stati scritti alcuni articoli sull’influenza del fenomeno definito GWS (Glass Fiber Skew) e sui requisiti minimi di perdita nei progetti di nuova generazione. Utilizzando le linee guida PCI Express come mezzo per tenere traccia di come impattano le frequenze più alte, in questo articolo cercherò di combinare gli elementi più importanti di questo nuovo fenomeno fisico. Il problema principale è che molti progettisti tendono a correggere “la rotta” solo a fronte di un fallimento progettuale importante.

È ormai passato molto tempo da quando ho iniziato ad occuparmi di integrità di segnale, erano gli anni ’90; Bill Hargin, a suo tempo Product Manager per il famosissimo simulatore di integrità di segnale HyperLynx, mi ha fatto muovere i primi passi in questo settore insegnandomi i rudimenti di base sull’argomento.

In questo primo periodo, molte società e diversi progettisti approcciavano l’argomento in modo reattivo, solo dopo aver subito più cicli di prototipazione o aver rilevato guasti sul campo, con i costi che ne conseguivano. Le problematiche che potevano essere individuate dai simulatori erano principalmente concentrate nel campo dell’integrità di segnale. Successivamente, nel corso del tempo l'elenco delle possibili problematiche analizzabili è cresciuto fino a includere la diafonia, i fattori di perdita in tutte le sue forme e infine la Power Integrity, disponibile oggi sia in DC che AC. Ho però notato che molti gruppi di progettazione odierni non considerano adeguatamente gli effetti sulla velocità dei segnali rispetto all’intreccio della fibra di vetro dei circuiti stampati; quindi, l’obiettivo di questo articolo è cercare di esplorare se i progettisti dovrebbero preoccuparsene in modo proattivo, dato il potenziale impatto di problemi apparentemente casuali che si potrebbero riscontrare quando il prodotto è ormai sul campo.

Background

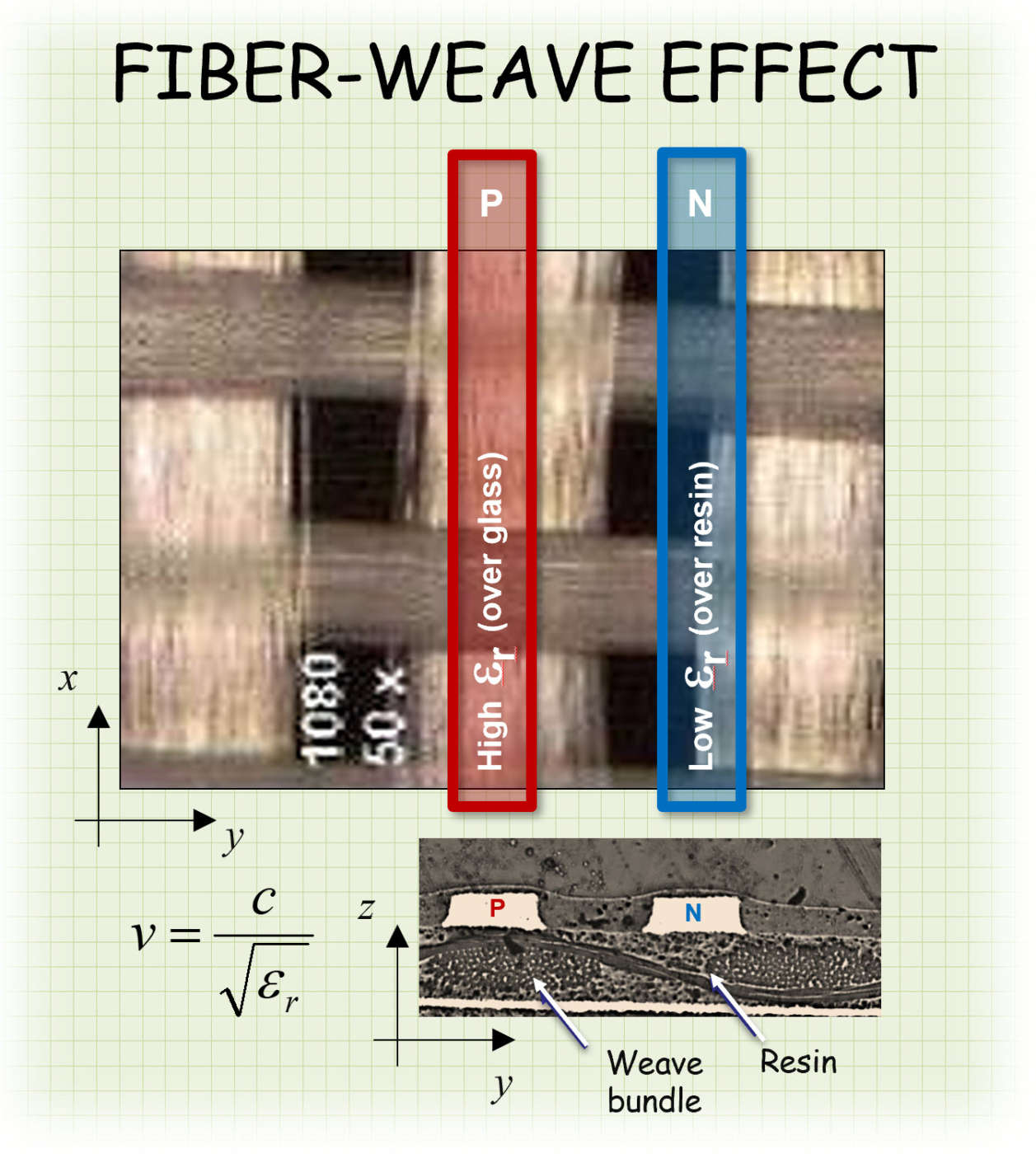

In pratica, l’effetto GWS e l'effetto già più conosciuto denominato FWE (Fiber Weave Effect), sono due aspetti dello stesso dominio. Più precisamente, si tratta dell'effetto della trama delle fibre di vetro e del relativo isolante sullo skew di segnali differenziali. Semantica a parte, l’effetto dell’intreccio della fibra di vetro su un segnale differenziale è causato da un microambiente di riferimento dei due segnali di una coppia fra di loro differente. Ciò è causato dal fatto che la struttura vetrosa ha un Dk (costante dielettrica) di circa 6,8 e la resina che compone il supporto ha un Dk di circa 3,0, considerando inoltre che può anche variare tra i vari tipi di resina. La Figura 1 mostra un segnale che è principalmente adiacente al vetro (P) nella miscela dielettrica resina-epossidica e l'altro segnale differenziale che attraversa una miscela di vetro e resina (N); il risultato sarà un Dk effettivo diverso per il due segnali, con conseguente variazione di impedenza e di velocità di propagazione.

L'allineamento semi-casuale dell'instradamento del segnale differenziale, mostrato in rosso e blu, rispetto all'allineamento del vetro sottostante, spesso determina velocità di propagazione medie diverse per ciascuna sezione della coppia differenziale. In questa immagine, il segnale differenziale positivo è su vetro (più lento) e il lato negativo ha una porzione significativa del percorso su resina (più veloce). Nella formula riportata, utilizzata per il calcolo e relativa al rapporto tra dielettrico e velocità, il fattore “C” è la velocità della luce.

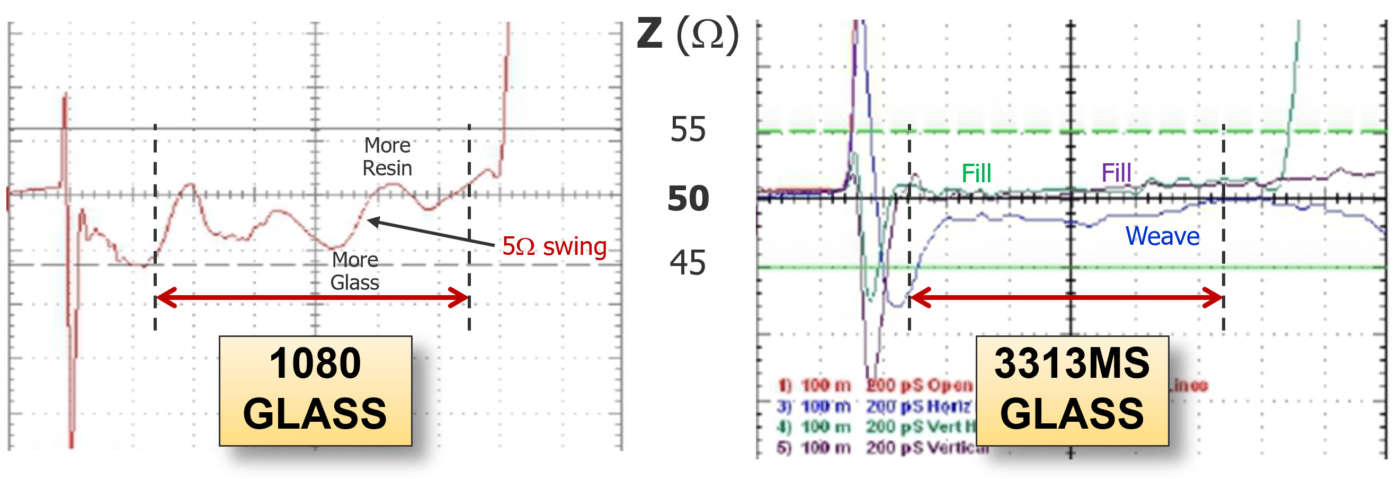

Lee Ritchey fornisce risultati di TDR (Time Domain Reflectometry) che mostrano questi effetti, mettendo a confronto come esempio due diversi tipologie di supporto: 1080 e 3313 (Figura 2). Da notare che l'impedenza è più uniforme nella tipologia 3313 rispetto alla 1080, sia quando i segnali sono paralleli alla trama della fibra di vetro (blu), sia quando sono paralleli all’ordito (verde e viola). Ciò si traduce in uno sfasamento tra le coppie molto contenuto. Le tipologie più note nel causare maggior sfasamento nei segnali differenziali sono le seguenti: 106, 1080, 2116 e 7628.

Il supporto 1080 mostra un'oscillazione di impedenza di circa 5 Ω. Con il supporto 3313MS, la variazione di impedenza è molto meno significativa, con la variazione parallela alla direzione della trama più significativa del segnale che corre parallela all’ordito.

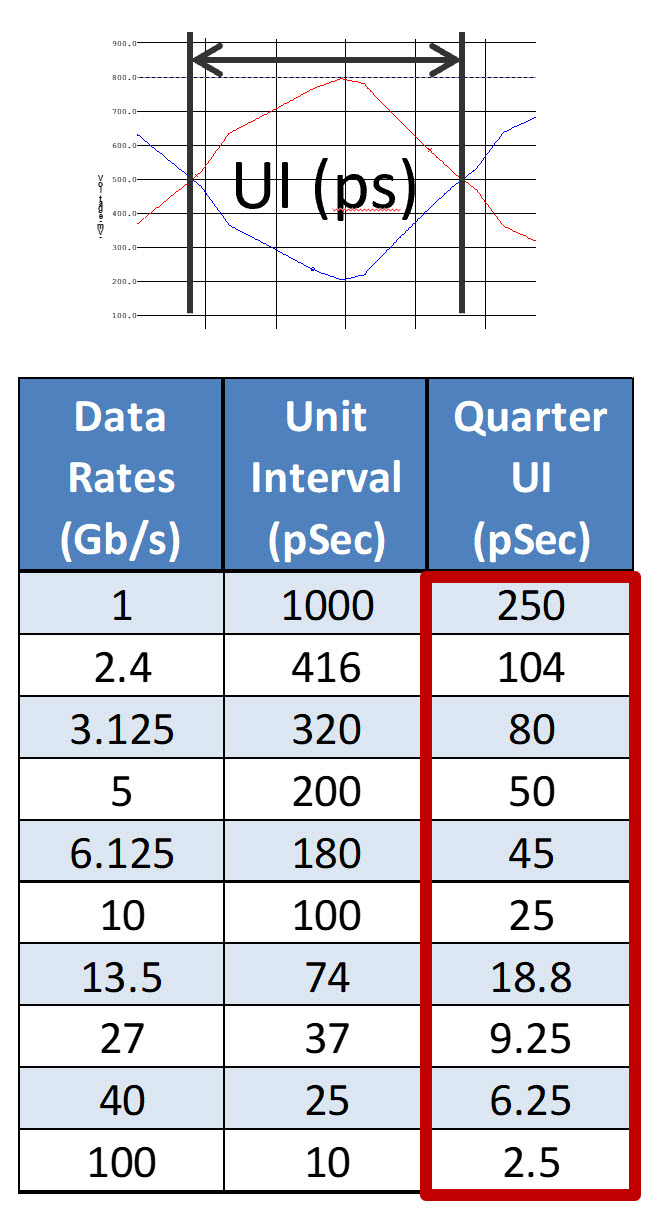

Ciascun standard e velocità differenziale del canale seriale ha una propria tolleranza per la variazione di fase (Skew). La maggior parte degli standard o dei produttori di chip offrono indicazioni sulla tolleranza allo skew, ma possiamo genericamente caratterizzare che la tolleranza di skew di un canale è descritta come circa il 25% dell’UI (Unit Interval) del flusso di bit; ad esempio, un segnale da 1 Gbps (500 MHz) avrebbe un UI di 1000 ps. Prendendo dunque in considerazione il valore del 25% come linea guida, si può ricavare una tolleranza massima di sfasamento pari a 250 ps. (Tabella 1) Questa tolleranza è effettivamente piuttosto ampia ed è il motivo per cui 20 anni fa la maggior parte dei progettisti non aveva necessità di preoccuparsi delle problematiche GWS. Le frequenze in gioco nei progetti attuali sono di molto superiori; prendendo come esempio un segnale da 10 Gbps (5 GHz), il suo UI è di 100 ps e la tolleranza massima di skew diminuisce fino a circa 25 ps. Diventa dunque ovvia la necessità di incominciare a considerare il fattore GWS come di primaria importanza.

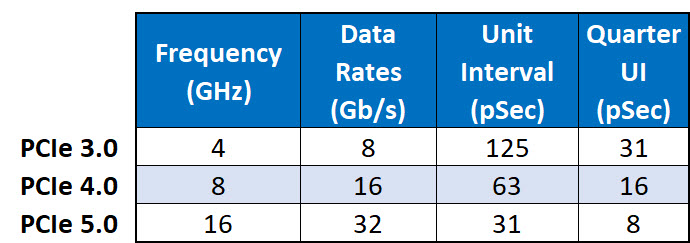

L’esempio di PCI Express e l’impatto del Glass-Weave Skew sui diagrammi a occhio

Potremmo far riferimento a qualsiasi standard bus, ma preferisco utilizzare il PCI Express, poiché è uno di quelli con cui molti progettisti hanno maggior familiarità. Utilizzando la stessa metodologia appena esposta, la Tabella 2 mostra che man mano che ci si muove dalle specifiche PCIe-3.0 alle specifiche PCIe-5.0, la tolleranza di skew si abbassa da 31 ps fino a 8 ps. A una qualsiasi di queste velocità, non si può più ignorare l’impatto del supporto, che può compromette in modo semi-casuale progetti altrimenti ben strutturati.

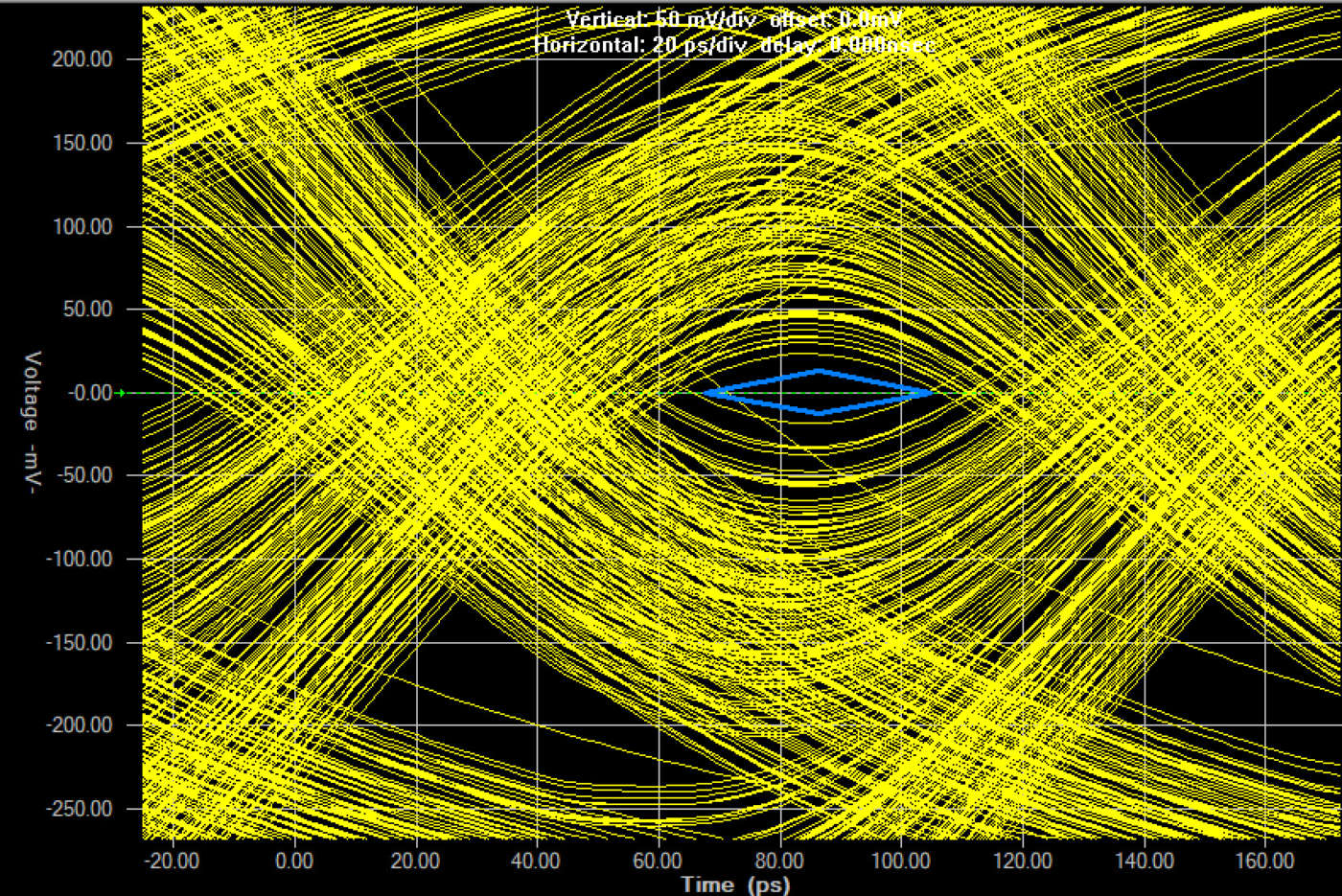

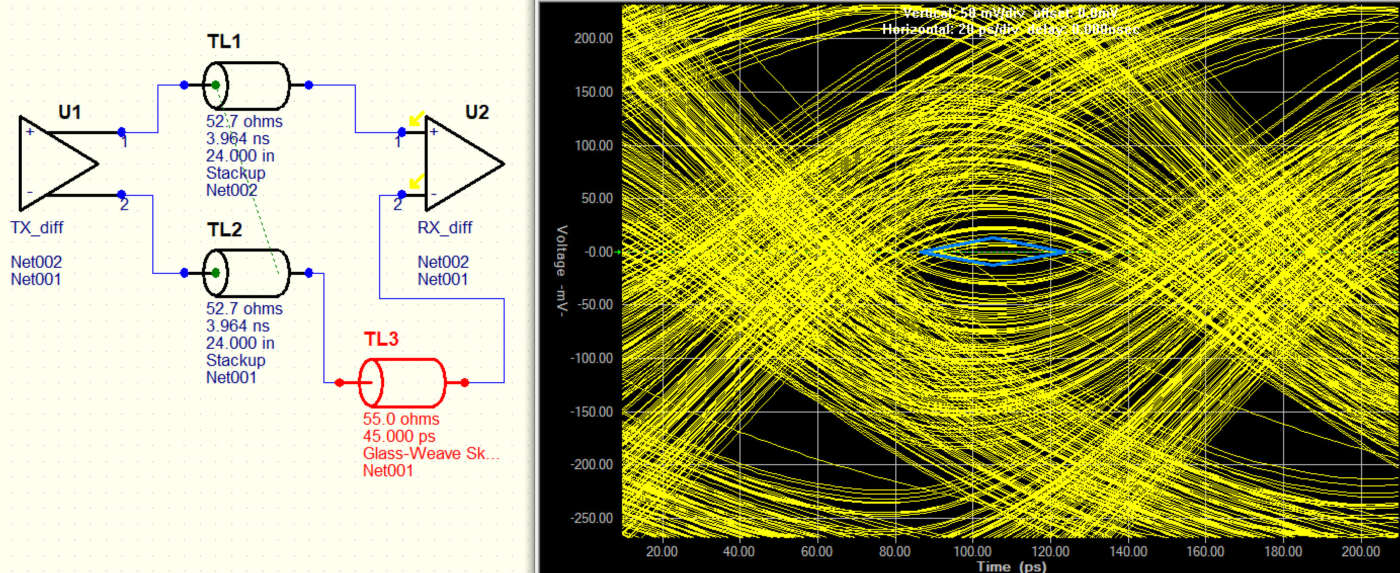

Diventa utile considerare cosa succede effettivamente nei diagrammi ad occhio. PCI Express 3.0 - La Figura 3 mostra i risultati della simulazione per un segnale a 8 Gbps utilizzando un materiale che ha causato problemi su piattaforme sviluppate su protocollo PCIe-3.0. Come si può vedere, l’area blu centrale (maschera di riferimento dell’occhio, relativa alle normative) è decisamente libera da attraversamenti di segnale, che è l’obiettivo di una simulazione con risultati positivi. Questo è un esempio ad alto livello dell'interazione tra frequenza, maschera di riferimento, diagramma ad occhio e skew dei segnali.

Secondo la Tabella 2, se introduciamo 45 ps di distorsione potenziale indotta dall'GWS in questo segnale differenziale, il risultato positivo appena visto dovrebbe risultare compromesso ed effettivamente, come riportato in Figura 4, si può chiaramente riscontare un’eccessiva “chiusura” dell’occhio. Questo ci permette anche di considerare valida la regola empirica del 25% dell’UI spiegata precedentemente. Inoltre, si deve considerare che il valore GWS può essere anche significativamente maggiore, a seconda della lunghezza dell'interconnessione e dell'allineamento semi-casuale tra le due linee in una coppia differenziale rispetto al tessuto vetroso sottostante.

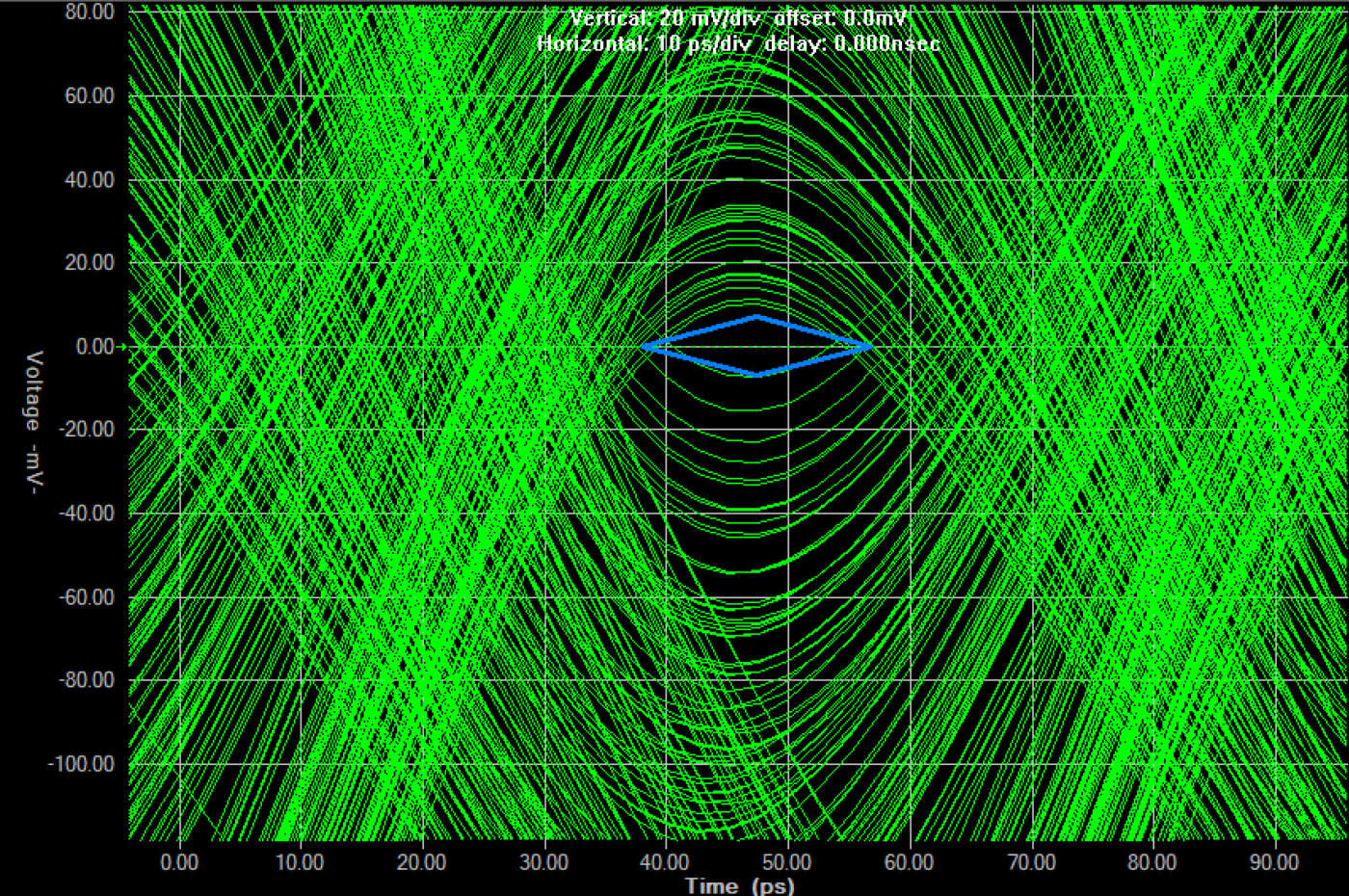

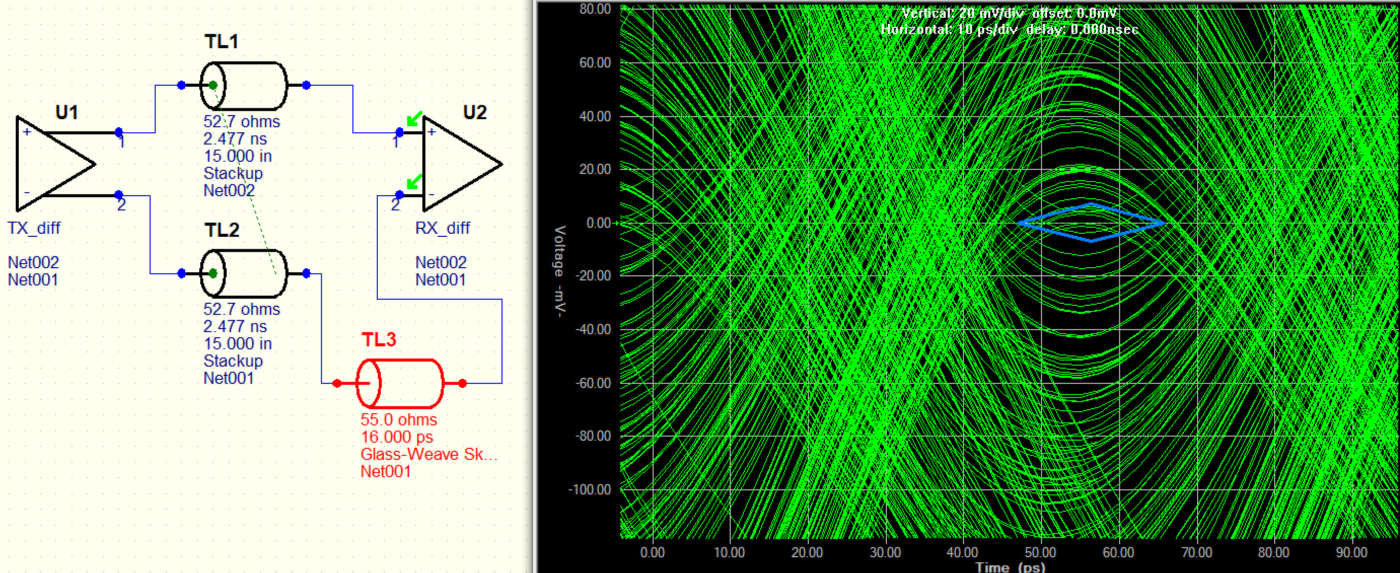

PCI Express 4.0 - Spostiamoci ora su un segnale PCIe-4.0, considerando un materiale di supporto più costoso e con minori perdite, facendo riferimento ad un segnale a 16 Gbps e adottando una maschera PCIe-4.0. La Figura 5 mostra il risultato. Si noti che la scala verticale è stata modificata, adattandosi ai requisiti di apertura più severi imposti dagli standard PCIe-4.0 rispetto alla versione 3.0.

Utilizzando la guida della Tabella 2, se introduciamo anche solo 16 ps di skew indotti dall'effetto GWS in questo segnale differenziale, possiamo verificare che anche in questo caso il risultato è compromesso, come visualizzato in Figura 6. La stessa quantità di skew che era perfettamente accettabile per gli standard PCIe-3.0, 16ps, è assolutamente inaccettabile per gli standard PCIe-4.0.

PCI Express 5.0 - Lo stesso esercizio di simulazione potrebbe essere eseguito con riferimento agli standard PCIe-5.0 o addirittura con frequenze ancora superiori. Come risulta ormai ovvio, ottenere simulazioni accettabili diventerebbe sempre più complesso proprio a causa, come abbiamo visto, della costante diminuzione della tolleranza di skew.

La riduzione dei rischi nasce dalla consapevolezza

Una delle considerazioni che possiamo fare rispetto all’effetto GWS è che in ogni caso i prototipi possono funzionare comunque correttamente, così come il 95% dei segnati sul 95% delle schede, indipendentemente dal possibile effetto GWS.

Purtroppo, nella situazione odierna di mercato, non ci si può permettere di avere una percentuale di rischio così alta e soprattutto non prevedibile proprio per la sua casualità, la quale è derivante dal posizionamento di un differenziale in una zona piuttosto che in un'altra, anche se solo leggermente spostata rispetto alla prima. I costi indotti da una prototipazione fallita o da un ritardo sul mercato sono sempre più alti e gli impatti sul successo di un progetto sempre più critici.

Gli elementi sistematici legati a questo effetto includono comunque la maggior parte dei percorsi di traccia che corrono paralleli alla trama e all’ordito nella struttura vetrosa adiacente. E c'è un elemento sistematico legato agli effetti di frequenza, ai margini operativi progettuali e al passo delle coppie differenziali sempre in relazione alla struttura vetrosa. Secondo il mio personalissimo parere, molti di questi effetti posso oggi essere messi sotto osservazione e controllati; sicuramente più di quanto i progettisti hardware possano rendersi conto.

È importante considerare che la riduzione dei rischi in un progetto ad alta velocità può iniziare con la consapevolezza di quanto questi effetti potrebbero essere qualcosa di cui preoccuparsi man mano che le frequenze in gioco aumentino. Spero sinceramente che le linee guida di base che ho sopra riportato possano rispondere alla domanda riportata nell’introduzione dell’articolo, almeno come spunto iniziale.

Ho comunque intenzione di approfondire l’argomento con altri articoli che pubblicheremo nei prossimi mesi, in cui vedremo alcuni suggerimenti per controllare e ridurre l’effetto GWS e alcuni dettami tecnici sui materiali di supporto ottimali per i circuiti stampati.

Note

- Lee Ritchey, Speeding Edge, “Minimizing Skew in High-Speed Differential Links,” dicembre 2015

- Bill Hargin, “Z-zero – Innovative PCB Stackup Design”, in Who Should Be Concerned about the Fiber-Weave Effect, February 2021